Verilog Reperesentation of Digital Logic 1

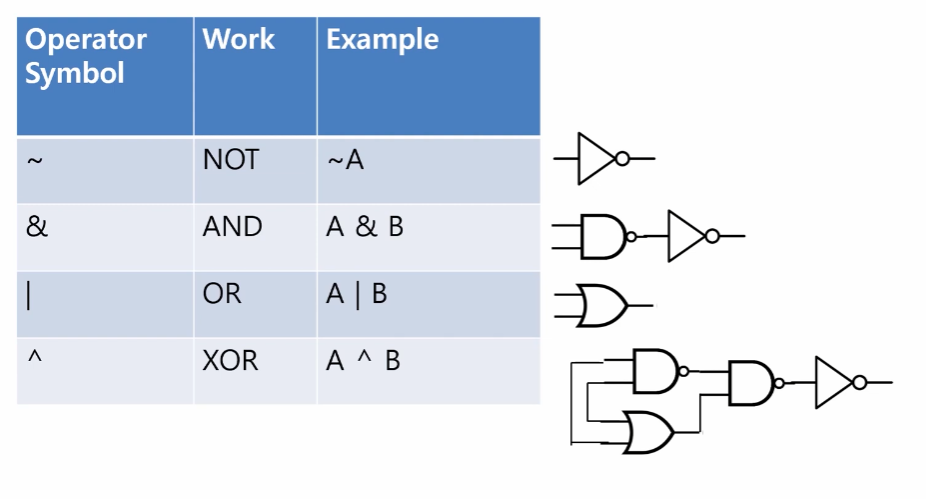

- Bitwise Operators of verilog

AND GATE = NAND + NOT으로 보면 된다.

XOR = NAND + NAND + OR + NOT로 구성

- NOT GATE

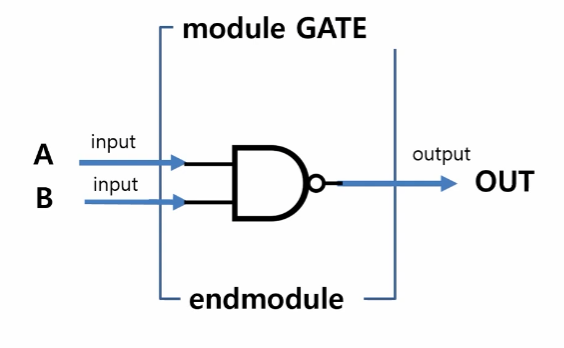

module은 c언어에서의 main문과 동일.

module ~ endmodule키워드로 범위를 지정.

위의 게이트는 input signal과 output signal이 하나씩 구성.

이것을 코드로 구성하게 되면 밑과 같게 된다.

module GATE(

input A,

output out

);

wire A;

wire out;

assign out = ~A;

endmodule

- OR GATE

INPUT signal 2개, OUTPUT signal 1개로 구성

module GATE(

input A,

input B,

output out

);

wire A;

wire B,

wire out;

assign out = A | B;

endmodule

- NOR GATE

OR GATE는 NOR + NOT게이트로 구성(물리적 회로는).

그러나 베릴로그에서는 OR + NOT게이트로 회로를 구성하게 된다.

-> NOR GATE를 표현해주는 키워드가 없기때문에 위와 같이 구성하게 된다.

-> 문법적으로 NOR GATE를 나타낼 수 없기때문에 ~( A | B )로 표현.

module GATE(

input A,

input B,

output out

);

wire A;

wire B,

wire out;

assign out = ~(A | B); //NOR GATE를 표현해주는 키워드가 없기때문에 이렇게 표현

endmodule베릴로그에서는 SYNTHESIS를 통해 위의 고충을 해결해준다. (C언어의 컴파일 가능 툴)

-> SYNTHESIS를 통해 게이트를 최적화해서 OR + NOT이 아닌 NOR로만 구성하게 해준다.

- NAND GATE, AND GATE

NAND GATE또한 NAND를 표현해주는 베릴로그 키워드가 없기때문에 SYNTHESIS를 통해 게이트를 최적화하여 회로상 NAND게이트를 표현.

//NAND GATE

module GATE(

input A,

input B,

output out

);

wire A;

wire B,

wire out;

assign out = ~(A & B); //NAND GATE를 표현해주는 키워드가 없기때문에 이렇게 표현

endmodule

//AND GATE

module GATE(

input A,

input B,

output out

);

wire A;

wire B,

wire out;

assign out = A & B;

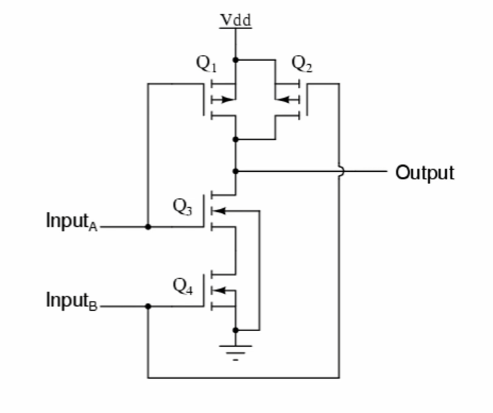

endmoduleNAND는 CMOS에서 그대로 구현가능. 트랜지스터로만 구성되어있다.

-> 반도체로 만들어질때에는 불필요한 NOT게이트는 생략이 되고 NAND GATE LOGIC을 수행하는 소자만 식각된다.

AND GATE는 NAND + NOT STAGE의 결합으로 만들어진다

-> propagation delay time(전파 지연 시간) 관점으로 생각해보면 실제로는 ~(A&B)가 A&B보다 빠르게 처리한다.

-> AND GATE는 NAND GATE + NOT GATE STAGE가 추가되기 때문에 NOT GATE의 propagation delay time이 추가되기 때문에 AND GATE의 전체적인 propagation delay time이 증가하게 된다.

LOGIC GATE들은 트랜지스터의 조합으로 만들어진다.

서로 비슷해보이는 LOGIC이더라도 트랜지스터의 갯수가 달라 소비전력이 다르다.

또한 트랜지스터 구성에 따른 (STAGE 구성에 따른) propagation delay time이 다르기 때문에 타이밍적인 요소들이 다르게 된다.

-> 설계자가 의도하지 않은 구성이 발생가능함.

-> 시스템 마진을 확보하기 위해 자신이 설계하고자 하는 시스템의 동작 주파수에 대한 정보들을 상기하고 타이밍적인 요소들을 고려해야한다.