조합회로, 순차회로, Multiplexer

vivado = 디자인 -> 시뮬레이션 -> 디바이스 3가지로 구분 가능

시뮬레이션 방법은 2가지

- 테스트벤치 (*.tb)

- TCL (*.tcl)

- 이상적인 주기펄스

이상적인 주기펄스는 두개의 에지(edge)로 구성

리딩에지(leading edge) = 상승에지

트레일링 에지(trailing edge) = 하강에지

하나의 주기가 된다

주파수 = 1초동안 진동한 횟수를 의미

주기 = 주기적인 파형이 1회 걸리는 시간

기본 멀티플렉서를 먹스라 부른다

기본 논리 게이트 = AND, OR, NOT, NOR, NAND, XOR, XNOR

비트단위 연산자 = Verilog HDL에서 디지털 논리 게이트회로의 기능을 담당하는 연산자로 5가지 종류(NOT AND OR XOR XNOR)가 사용

- 연산자

- & = 비트 단위로 AND연산

- | = 비트 단위로 OR연산

- ^ = 비트 단위로 XOR연산

- ~ = 단항 연산자로서 피연산자의 모든 비트를 반전

- ~^, ^~ = Bitwise XNOR

조건 연산자는 MUX에서 사용

- 기본 논리 게이트1

`timescale 1ns / 1ps // 기본 단위를 ns로 성정

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2023/06/01 16:41:06

// Design Name:

// Module Name: add

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module add(

input a, input b,

output c_and,

output c_or,

output c_not,

output c_nand,

output c_nor,

output c_xor,

output c_xnor

);

assign c_and = a&b;

assign c_or = a | b;

assign c_not = ~a;

assign c_nand = ~(a&b);

assign c_nor = ~(a | b);

assign c_xor = a^b;

assign c_xnor = ~(a^b);

endmodule

시뮬레이션을 저장해두는 것이 좋다

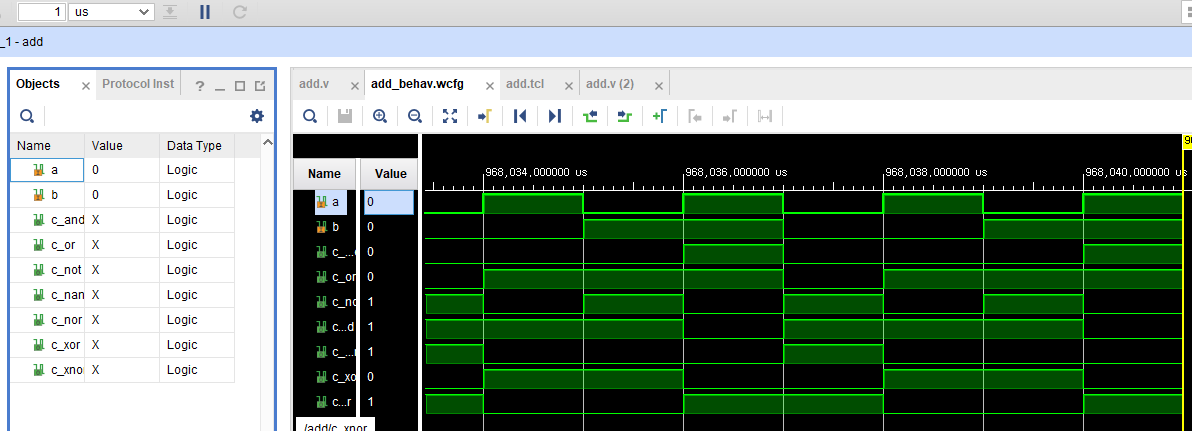

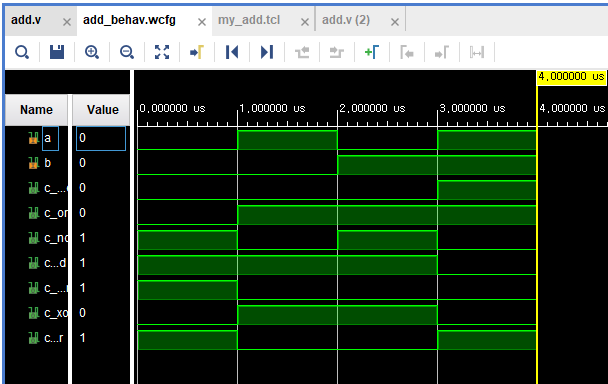

시뮬레이션 창을 띄우면 Objects창에서 input 소자들의 입력 값을 넣어줄 수 있다.

Force constant = 단일 입력

Force clock = 클럭 단위 입력

정상적으로 시뮬레이션 나오는 것 확인 가능

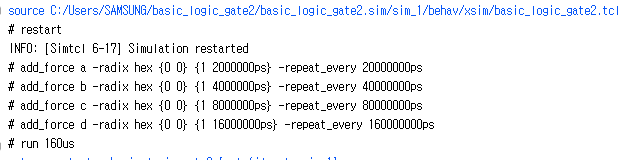

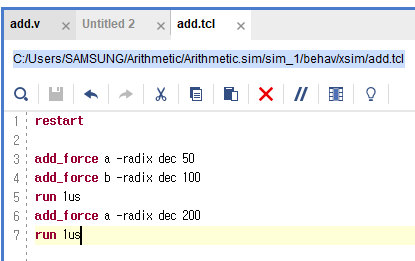

- tcl파일을 이용한 시뮬레이션 변경

tcl파일을 이용하여 코드에서 변경된 내용을 시뮬레이션에 적용가능

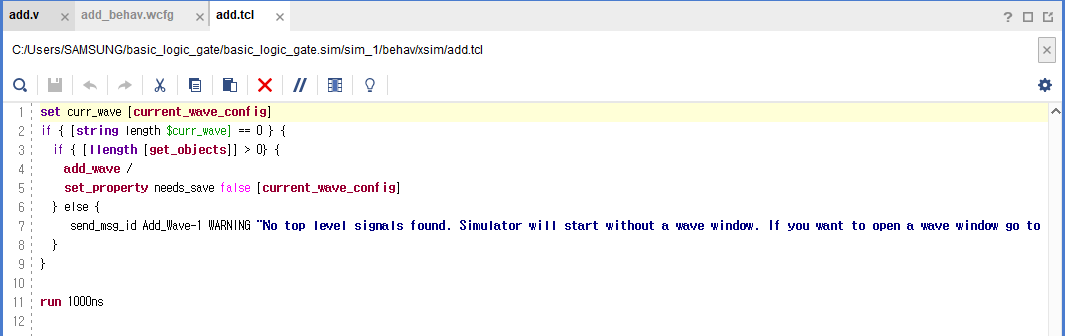

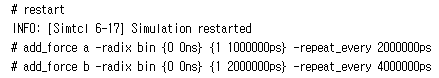

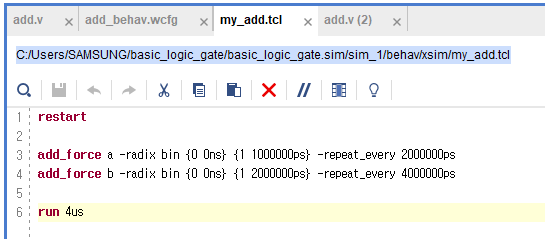

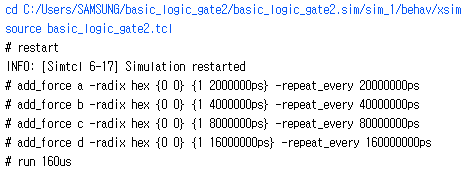

add force 에서 period등을 정해주는데, 이 과정을 tcl 코드에서 수정하여 console창을 이용하여 시뮬레이션에 적용가능

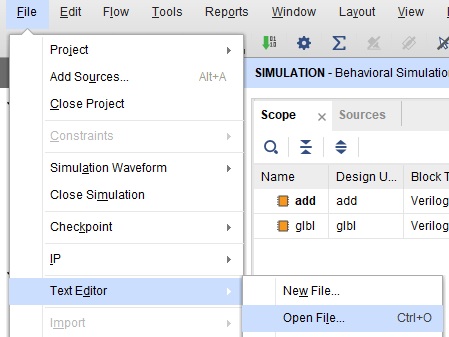

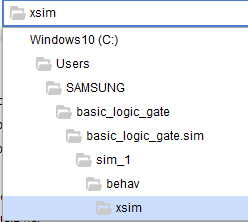

해당 경로로 들어가게 되면 파일.tcl 이 있는 것을 확인할 수 있다.

해당 tcl파일을 오픈 후

tcl파일 안의 내용을 지운 후, (저장X) 오른쪽 마우스를 클릭하여 Save File As로 새로운 tcl파일을 생성한다.

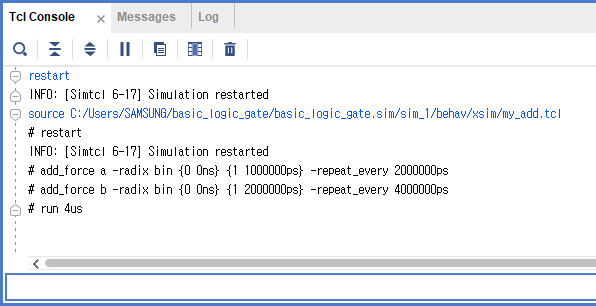

생성 후, 시뮬레이션 창에서 restart 클릭 후, 시뮬레이션을 돌리면 밑의 console에서 실행 시뮬레이션 코드가 뜬다.

해당 시뮬레이션코드를 tcl파일에 적은 후, Tcl console창에 tcl의 주소를 입력하면 tcl파일에서 입력한 시뮬레이션 코드 시뮬레이션에 적용가능

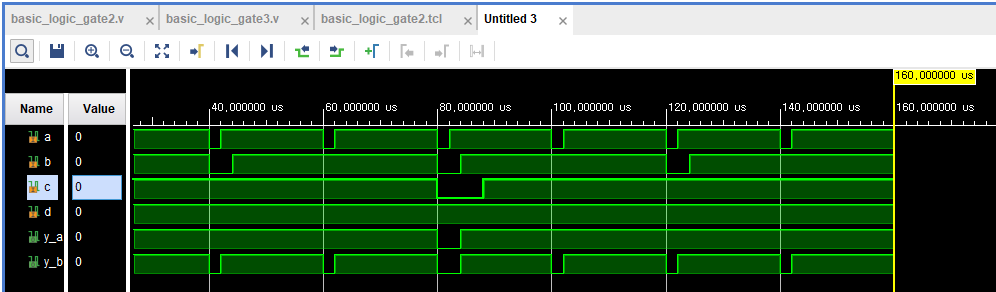

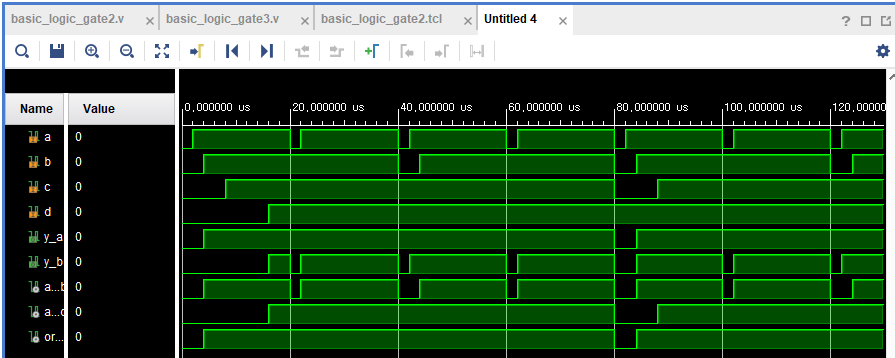

- 기본 논리 게이트2

//Design Source - basic_logic_gate2

module basic_logic_gate2(a,b,c,d,y_a,y_b );

input a,b,c,d;

output y_a,y_b;

assign y_a = (a&b) | (c&d);

assign y_b = a&(b|c) & d;

endmodule//Design Source - basic_logic_gate3

module basic_logic_gate3(a,b,c,d,y_a,y_b);

input a,b,c,d;

output y_a,y_b;

wire and_ab;

wire and_cd, or_bc;

assign and_ab = a&b;

assign and_cd = c&d;

assign or_bc = b|c;

assign y_a = and_ab | and_cd;

assign y_b = a&or_bc & d;

endmodule

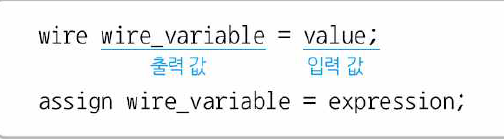

- wire

- 조합회로의 결과로 생성된 신호가 module내부에서만 이용될 때 선언 가능

- Module 내에서 생성되는 조합회로의 결과 신호들중에서 출력포트 신호가 아닌 내부적으로만 사용되는 신호

- 조합회로의 결과만 받을 수 있을 뿐, 플립플롭, 카운터 및 레지스터와 같은 유지하는 순차회로 결과 신호는 사용 불가

- assign - 게이트간의 연결 가능, 모듈간의 연결 또한 가능 / wire - 게이트간의 연결 가능, 모듈간의 연결은 불가능

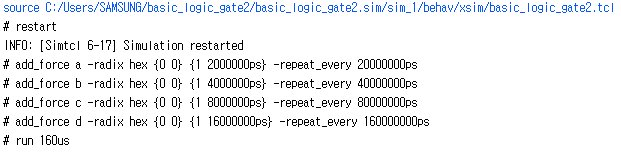

코드 입력 후, tcl파일에서 밑의 코드 입력하여 Tcl console창에 실행

tcl실행은

- cd를 이용하여 해당 tcl파일 위치로 이동 후, source 명령어를 이용하여 tcl코드 실행

- 전체 경로를 입력 후, source명령어를 이용하여 tcl코드 실행

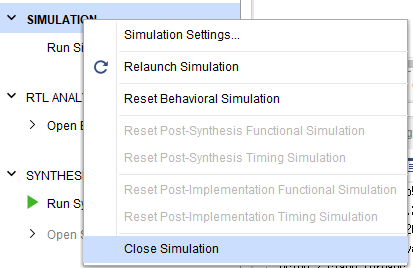

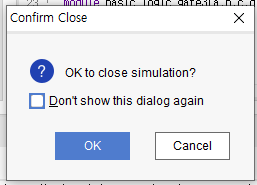

- 시뮬레이션 종료

1)

2)

1), 2) 둘 중 하나의 과정 선택 후, 시뮬레이션 종료 가능

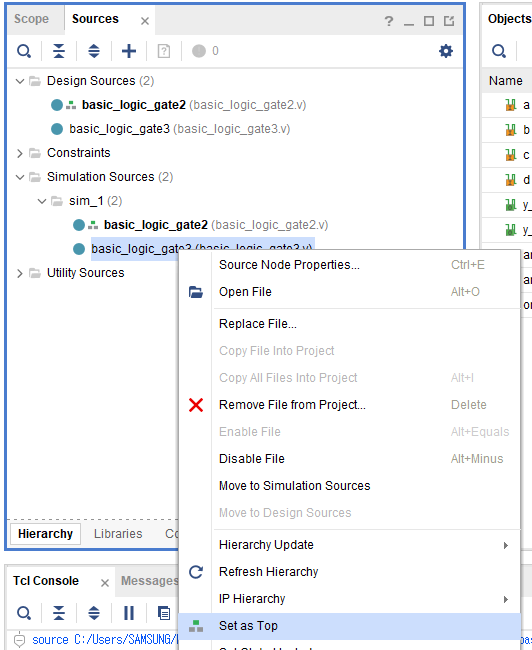

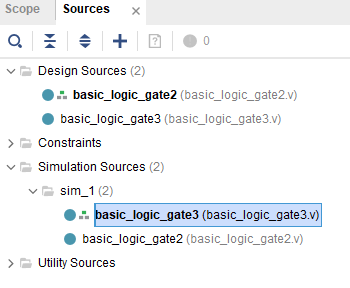

- tcl 파일을 이용하여 새로운 소스파일 시뮬레이션 실행

실행시킬 시뮬레이션을 Set as Top시켜 올려준다.

실행시킬 tcl 소스코드의 주소를 Tcl console창에 입력하여 실행한다.

다른 베릴로그 소스코드이지만, tcl소스코드를 이용하여 정상적으로 시뮬레이션 실행 확인

- module

- Verilog HDL을 구성하는 가장 기본적인 구성 단위

- 첫 번째 줄에 module 이름과 인자 나열

- 다음 줄에 입출력 타입과 포트의 비트 수가 정의

- 'endmodule'로 module 정의 종료

- 연속 할당문

- 동시에 연속적으로 실행되며 순서에 영향을 받지 않음

- 일반적으로 always block 또는 wire가 선언될 때 값을 할당하는데 사용

- assign문을이용하여 입력이 바뀔 때 출력에 새로운값 할당

구조적모델 = 기본 연산자를 이용하여 구성한 모듈

동작적 모델 = 조건문을 이용하여 구성한 모듈

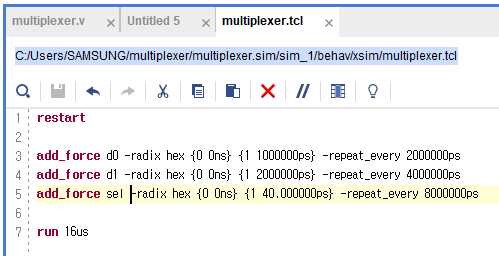

- Multiplexer

- [2x1, n=1] multiplexer

-> Multi-bit를 Bus로 사용하는 Multiplexer logic에 대한 verilog HDL구현

module multiplexer(

input d0,

input d1,

input sel,

output y_a,

output y_b

);

assign y_a = (~sel & d0) | (sel & d1);

assign y_b = (sel == 0) ? d0 : d1 ;

endmodule

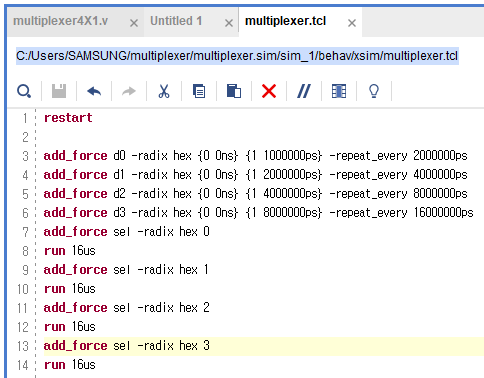

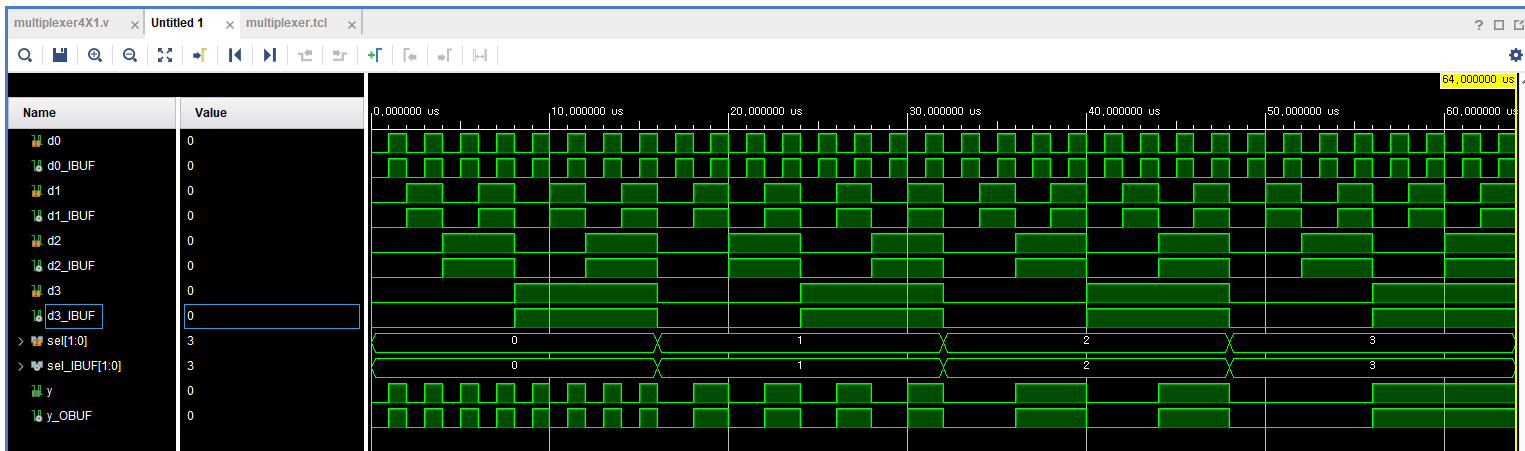

- [4x1, n=2] multiplexer 1

-> Input[Sel]에 Multi-bit를 Bus로 사용하는 Multiplexer logic에 대한 verilog HDL구현

module multiplexer4X1(

input d0,

input d1,

input d2,

input d3,

input [1:0] sel,

output y

);

assign y = (sel == 0) ? d0 :

(sel == 1) ? d1 :

(sel == 2) ? d2 :

d3 ;

endmodule

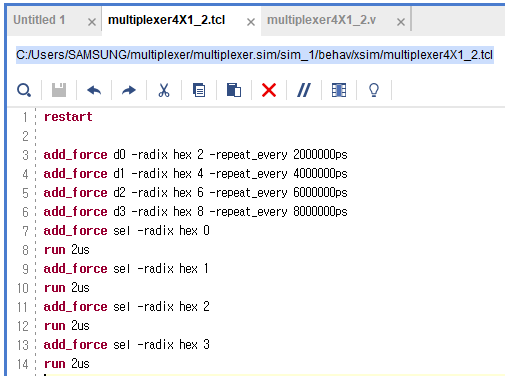

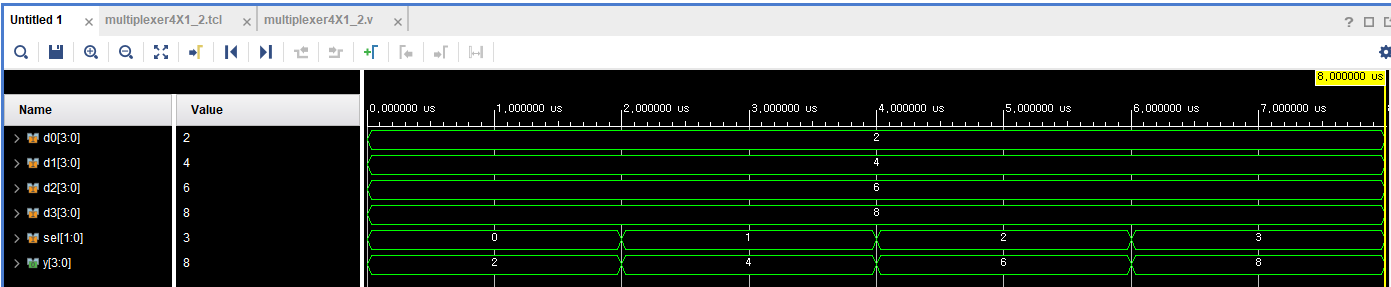

- [4x1, n=2] multiplexer 2

-> Input과 Output에 Multi-bit를 Bus로 사용하는 Multiplexer logic에 대한 verilog HDL구현

module multiplexer4X1_2(

input [3:0] d0,d1, d2, d3,

input [1:0] sel,

output [3:0] y

);

assign y = (sel == 0) ? d0 :

(sel == 1) ? d1 :

(sel == 2) ? d2 :

d3 ;

endmodule

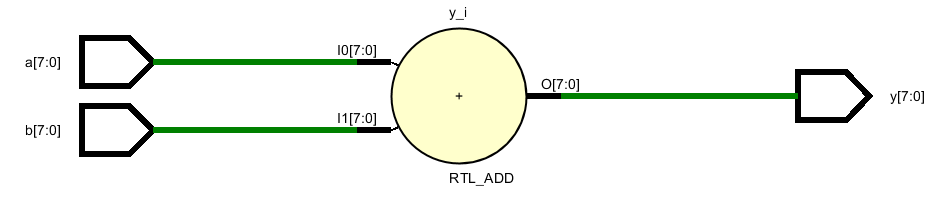

- 산술 연산

디지털회로에서 연산을 수행할 때 Signed (최상위 비트를 sign bit로 사용)연산과 Unsigned(모든 비트를 크기 값으로 사용)연산으로 구분하여 설계

덧셈은 8비트 연산을 한다

- 덧셈회로 -> a+b

module add(

input [7:0] a,

input [7:0] b,

output [7:0] y

);

assign y = a+b;

endmodule

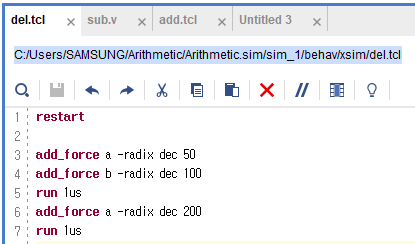

- 뺄셈회로 -> a-b

module sub(

input [7:0] a,

input [7:0] b,

output [7:0] y

);

assign y = a-b;

endmodule

a = 50 / b = 100 => a-b = -50이 아니라 206이 나오게 된다.

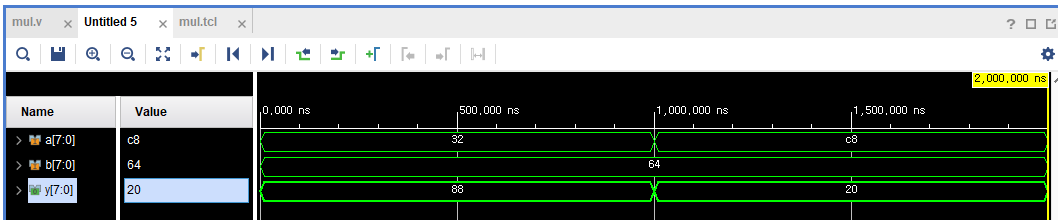

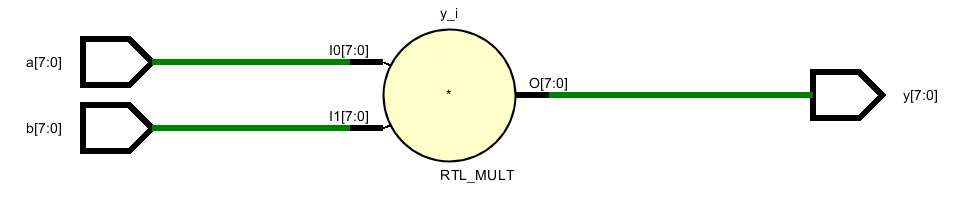

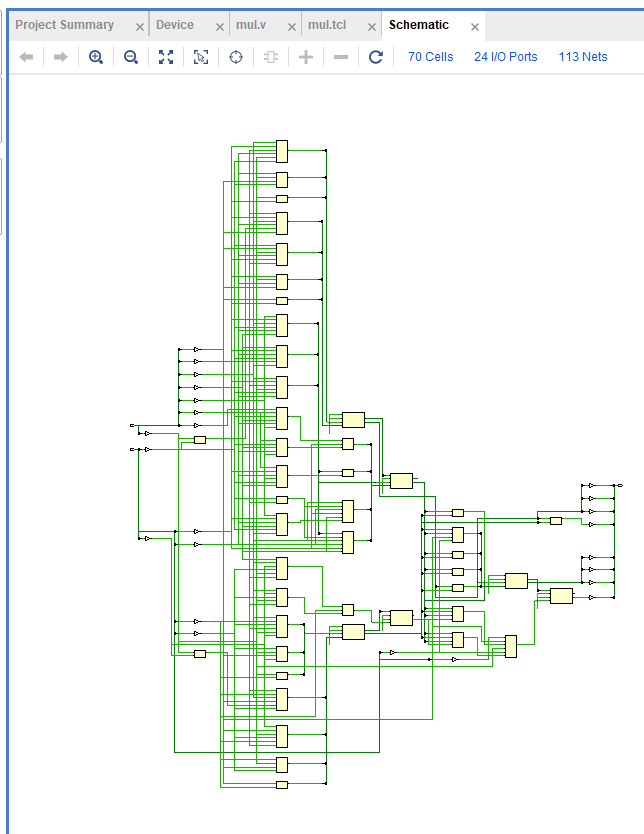

- 곱셈회로

module mul(

input [7:0] a,

input [7:0] b,

output [7:0] y

);

assign y = a*b;

endmodule

- 나눗셈회로

module div(

input [7:0] a,

input [7:0] b,

output [7:0] y

);

assign y = a/b;

endmodule

- Hierarchy

module Hierarchy(

input [7:0] a_a, b_b,

input [1:0] sel,

output [7:0] y_out

);

wire [7:0] y_a,y_s,y_m,y_m;

arith4u_arith_hier_0

(

.a (a_a),

.b (b_b),

.y_add (y_a),

.y_sub (y_s),

.y_mul (y_m),

.y_div (y_d)

);

assign y_out = (sel == 0) ? y_a:

(sel == 1) ? y_s:

(sel == 2) ? y_m:

y_d;

endmodule