FPGA/HDLBits

Wire decl

장영현

2023. 6. 8. 23:07

728x90

Problem Statement

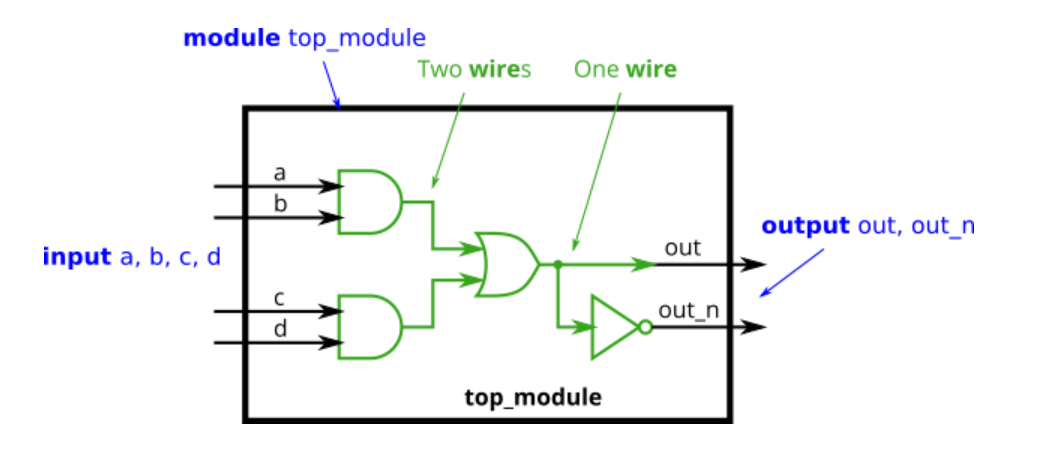

Implement the following circuit. Create two intermediate wires (named anything you want) to connect the AND and OR gates together. Note that the wire that feeds the NOT gate is really wire out, so you do not necessarily need to declare a third wire here. Notice how wires are driven by exactly one source (output of a gate), but can feed multiple inputs.

If you're following the circuit structure in the diagram, you should end up with four assign statements, as there are four signals that need a value assigned.

(Yes, it is possible to create a circuit with the same functionality without the intermediate wires.)

//1

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire Two_wires_1;

wire Two_wires_2;

wire One_wire;

assign Two_wires_1 = a & b;

assign Two_wires_2 = c & d;

assign One_wire = Two_wires_1 | Two_wires_2;

assign out = One_wire;

assign out_n = ~One_wire;

endmodule

//2

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

assign out = (a & b) | (c & d) ;

assign out_n = ~((a & b) | (c & d));

endmodule

//3

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire Two_wires_1, Two_wires_2, One_wire;

assign Two_wires_1 = a & b;

assign Two_wires_2 = c & d;

assign out = Two_wires_1 | Two_wires_2 ;

assign out_n = ~(Two_wires_1 | Two_wires_2);

endmodule

module top_module (

input in, // Declare an input wire named "in"

output out // Declare an output wire named "out"

);

wire not_in; // Declare a wire named "not_in"

assign out = ~not_in; // Assign a value to out (create a NOT gate).

assign not_in = ~in; // Assign a value to not_in (create another NOT gate).

endmodule // End of module "top_module"