FPGA/HDLBits

Module cseladd

장영현

2023. 6. 10. 19:04

728x90

Problem Statement

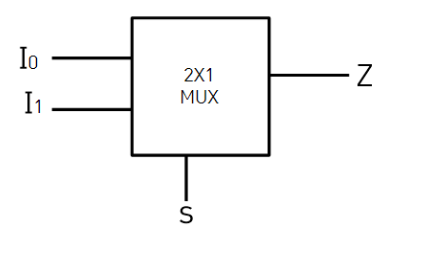

In this exercise, you are provided with the same module add16 as the previous exercise, which adds two 16-bit numbers with carry-in and produces a carry-out and 16-bit sum. You must instantiate three of these to build the carry-select adder, using your own 16-bit 2-to-1 multiplexer.

Connect the modules together as shown in the diagram below. The provided module add16 has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout1, cout2, cout3;

wire [15:0] sum1, sum2;

reg [15:0] mux_out;

add16 instance1 (a[15:0], b[15:0], 1'b0, sum[15:0], cout1);

add16 instance2 (a[31:16], b[31:16], 1'b0, sum1, cout2);

add16 instance3 (a[31:16], b[31:16], 1'b1, sum2, cout3);

always @ (*) begin

case (cout1)

1'b0 : mux_out = sum1;

1'b1 : mux_out = sum2;

endcase

end

assign sum = {mux_out, sum[15:0]};

endmodule

3개의 전가산기와 2x1 MUX를 이용하는 회로 문제

2x1 멀티플렉서를 always문을 이용하여 생성하고 case문을 이용하여 조건을 설정 후, 전가산기 sum과 멀티플렉서 출력을 합치면 된다.