2024. 1. 2. 14:07ㆍ개인공부/RTL

- Valid, Ready Handshake

- Valid, Ready Handshake는 모듈 간의 명확한 데이터 전송을 위한 인터페이스

- 송신자와 수신자가 모두 준비되었을 때만 데이터가 전송되는 동기화된 통신방법

- 데이터를 전송하기 전에 상호간의 정해진 format에 맞춰 데이터를 전송해야 한다.

- 이 과정을 하지 않게 되면 데이터 전송 간의 유실 발생

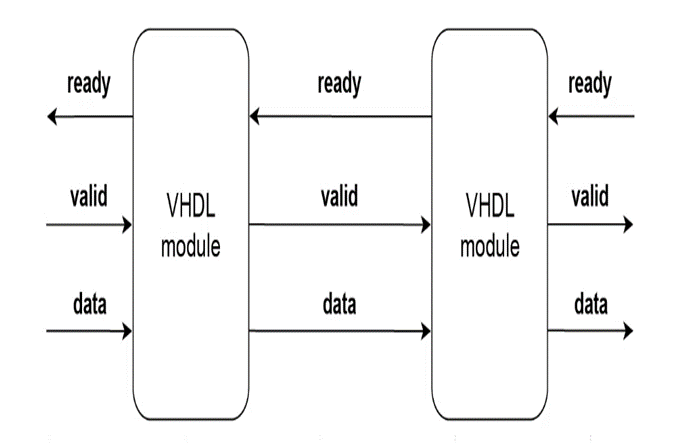

- Valid Ready Handshake Basic Module

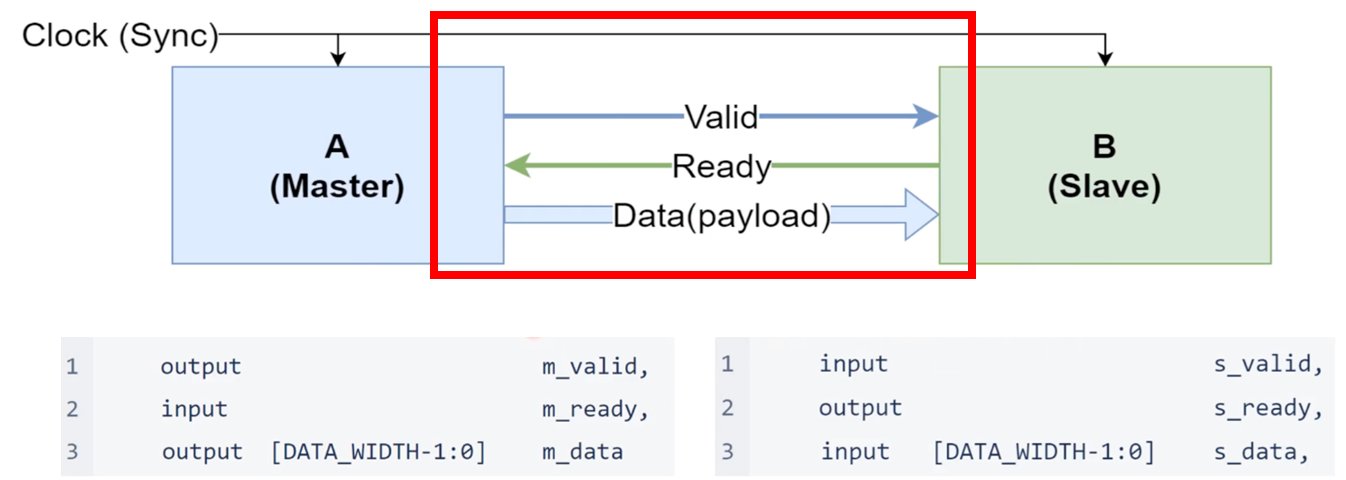

- Master Module에서 Valid 신호 출력, Slave Module에서 Ready 신호 출력

- 양방향 통신이 불가능하기 때문에 A->B가 아닌 B->A로 데이터를 전송하려면 Valid, Ready, Data 채널을 하나 더 만들어야 한다.

( A->B 데이터 전송을 위한 Valid, Ready, Data 채널 존재 / B->A 데이터 전송을 위한 Valid, Ready, Data 채널이 따로 존재)

-> B->A로 데이터 전송 format을 이루게 된다면 B는 Master, A는 Slave가 된다.

- Valid Ready Handshake의 기본 구성은 Master - Handshake module - Slave로 구성

- Valid Ready Handshake Basic module에선 D-FF으로 구성

- Data는 Master -> Slave로 전송된다.

- s_ready, CE 신호가 연결되어 있어, s_ready 신호가 FF의 저장 여부를 결정한다.

-> FF의 값이 0이기 때문에, 뒷 단의 여부에 관계 없이 FF에 값을 저장할 수 있는 상태

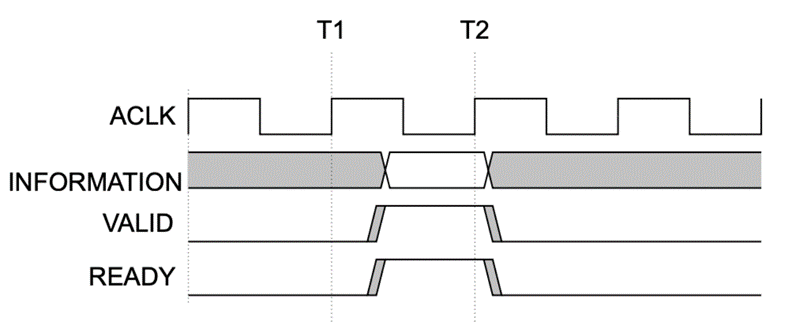

- Valid Ready Handshake 인터페이스 과정

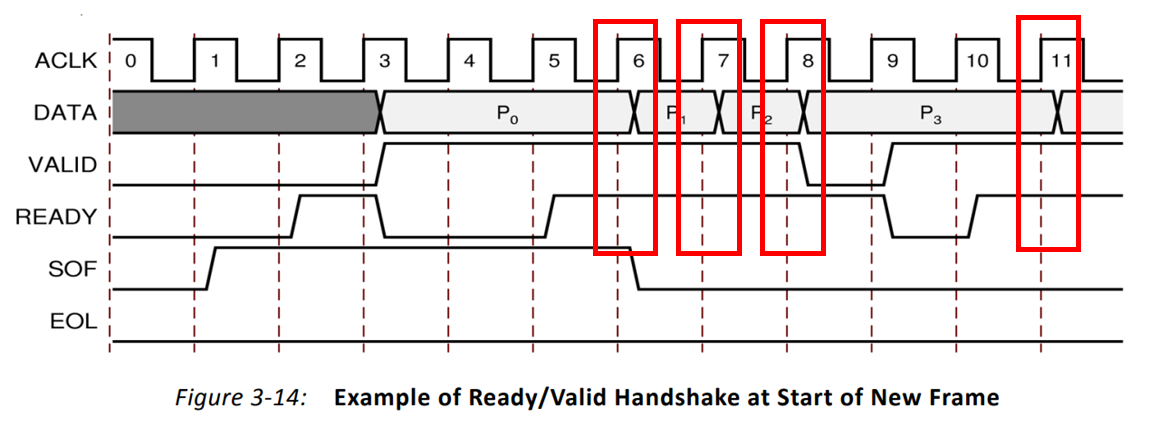

- Valid : 송신측에서 Data 전송이 완료되었는지 나타내는 Signal

- Ready : 수신측에서 Data를 받을 수 있는지 알려주는 Signal

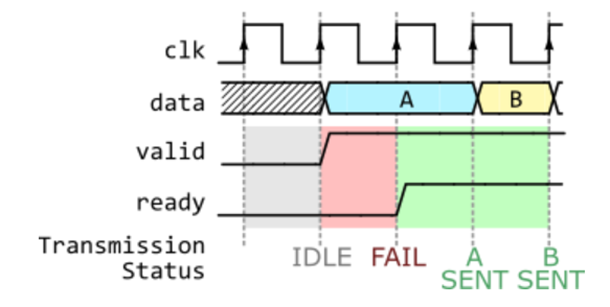

- 송신자의 Valid와 수신자의 Ready 신호가 high인 상태에서 Data 전송

| State | Valid | Ready | Explanation |

| IDLE | 0 | 0 | 송신측, 수신측 전부 데이터를 전송하지 않는 상태 |

| Wait for Valid | 0 | 1 | 수신측은 Data를 받을 준비가 되었지만, 송신측은 Data를 전송할 준비가 되어있지 않은 상태 |

| Wait for Ready | 1 | 0 | 송신측은 Data를 전송할 준비가 되었지만, 수신측은 Data를 받을 준비가 되어있지 않은 상태 |

| Transfer | 1 | 1 | 송신측에서 Valid 신호를 보내고, 수신측에도 Ready 신호를 보내어 서로간의 Data 전송 준비가 완료된 상태. 이상태에서 Data가 전송된다. |

- 이 Valid Ready 신호는 AMBA AXI의 모든 Channel에서 공통으로 가지고 있다.

- AXI4-Lite 버스의 신호선 (기존의 AXI4는 많은 신호선을 가지고 있으므로, 간략화시킨 AXI4-Lite를 가져왔다.)

- 각 Channel별로 Valid-Ready Handshake를 위한 신호선을 가진다.

- ADDR : address / RESP : reasponse / PROT : protection / STRB : Valid한 신호선이 어느곳인지 판별

- 이때, Deadlock을 막기 위해, Valid와 Ready 신호가 종속적으로 동작하지 않는다.

- Valid와 Ready가 high인 상태에 Data가 전송되는 것을 확인

-> ACLK가 Rising edge일 때, 다음 Data로 변경