2023. 6. 7. 11:23ㆍ[Harman] 세미콘(semiconductor) 아카데미-반도체설계/Verilog를 이용한 RTL 시스템 반도체 설계

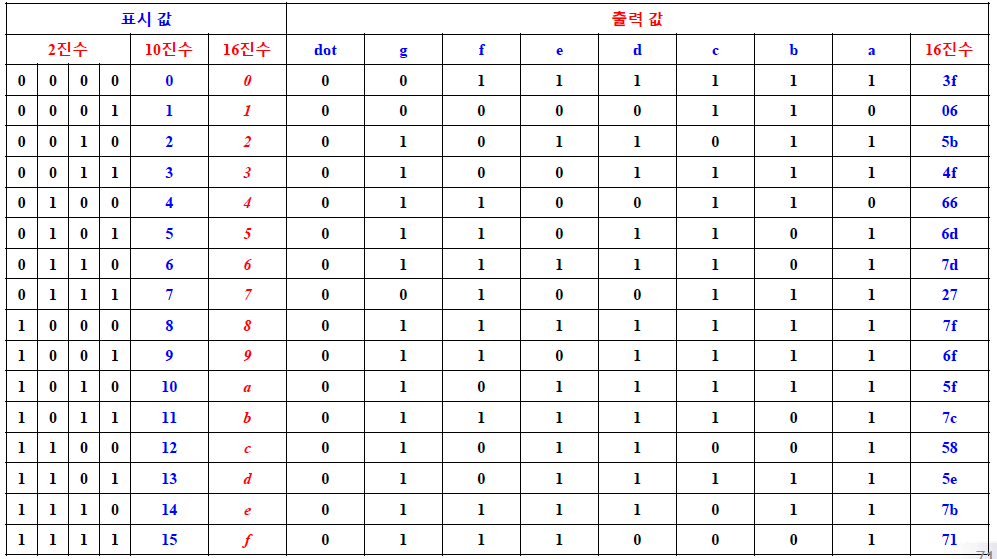

- 7 Segment Decoder

회로 크기와 지연시간 확인

-> Conditional Operator : din 값이 0과 같은 가를 판별하는 판단 조건 문으로 사용

-> Assign sseg_d = (판단문) ? [참일 때의 전달 값] : [거짓일 때의 전달 값]

Verilog HDL 에서 상수 값 설정

- Verilog HDL 에서 상수 값을 설정하거나 비교할 때 별도 표시가 없으면 10진수에 해당하는 값으로 인식

- 필요에 의해 2진수 혹은 16진수 값을 설정하거나 비교해야 할 경우, 진법 설정 및 값 설정

module segment_decoder(

input [3:0] x_seg,

output [7:0] y_seg

);

assign y_seg = (x_seg == 4'h0) ? (8'h40) :

(x_seg == 4'h1) ? (8'h79) :

(x_seg == 4'h2) ? (8'h24) :

(x_seg == 4'h3) ? (8'h30) :

(x_seg == 4'h4) ? (8'h19) :

(x_seg == 4'h5) ? (8'h12) :

(x_seg == 4'h6) ? (8'h02) :

(x_seg == 4'h7) ? (8'h58) :

(x_seg == 4'h8) ? (8'h00) :

(x_seg == 4'h9) ? (8'h10) :

(x_seg == 4'ha) ? (8'h20) :

(x_seg == 4'hb) ? (8'h03) :

(x_seg == 4'hc) ? (8'h27) :

(x_seg == 4'hd) ? (8'h21) :

(x_seg == 4'he) ? (8'h04) :

(8'h0e) ;

endmodule

//tcl 코드

restart

add_force x_seg[0] -radix bin {0 0us} {1 1us} -repeat_every 2us

add_force x_seg[1] -radix bin {0 0us} {1 2us} -repeat_every 4us

add_force x_seg[2] -radix bin {0 0us} {1 4us} -repeat_every 8us

add_force x_seg[3] -radix bin {0 0us} {1 8us} -repeat_every 16us

run 16us

Bitstream

//Basys3_Master.xdc

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports {x_seg[0]}]

set_property -dict { PACKAGE_PIN V16 IOSTANDARD LVCMOS33 } [get_ports {x_seg[1]}]

set_property -dict { PACKAGE_PIN W17 IOSTANDARD LVCMOS33 } [get_ports {x_seg[2]}]

set_property -dict { PACKAGE_PIN W16 IOSTANDARD LVCMOS33 } [get_ports {x_seg[3]}]

set_property -dict { PACKAGE_PIN W7 IOSTANDARD LVCMOS33 } [get_ports {y_seg[0]}]

set_property -dict { PACKAGE_PIN W6 IOSTANDARD LVCMOS33 } [get_ports {y_seg[1]}]

set_property -dict { PACKAGE_PIN U8 IOSTANDARD LVCMOS33 } [get_ports {y_seg[2]}]

set_property -dict { PACKAGE_PIN V8 IOSTANDARD LVCMOS33 } [get_ports {y_seg[3]}]

set_property -dict { PACKAGE_PIN U5 IOSTANDARD LVCMOS33 } [get_ports {y_seg[4]}]

set_property -dict { PACKAGE_PIN V5 IOSTANDARD LVCMOS33 } [get_ports {y_seg[5]}]

set_property -dict { PACKAGE_PIN U7 IOSTANDARD LVCMOS33 } [get_ports {y_seg[6]}]

set_property -dict { PACKAGE_PIN V7 IOSTANDARD LVCMOS33 } [get_ports {y_seg[7]}]

- 순차 논리 회로

- 순차 회로 = Clock이 발생했을 때 출력이 변하는 회로.

- 비동기 set혹은 reset을 제외한 모든 입력의 변화는 clock이 발생하지 않는 한 출력에 영향을 주지 못한다.

- D - FlipFlop = 순차회로의 기본이 되는 블록으로 다른 순차회로들은 D-Flip Flop 과 조합회로들이 결합된.형태도 동작

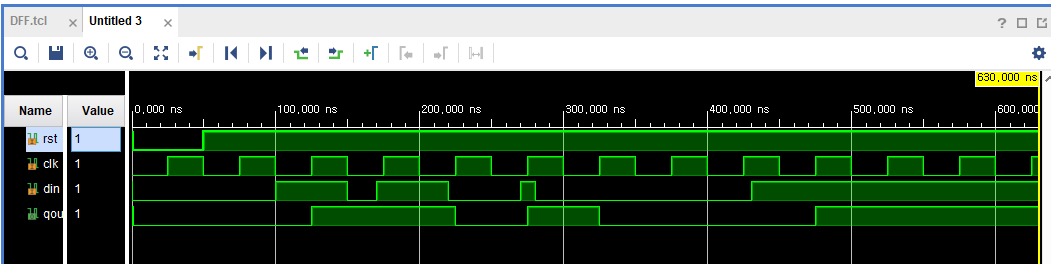

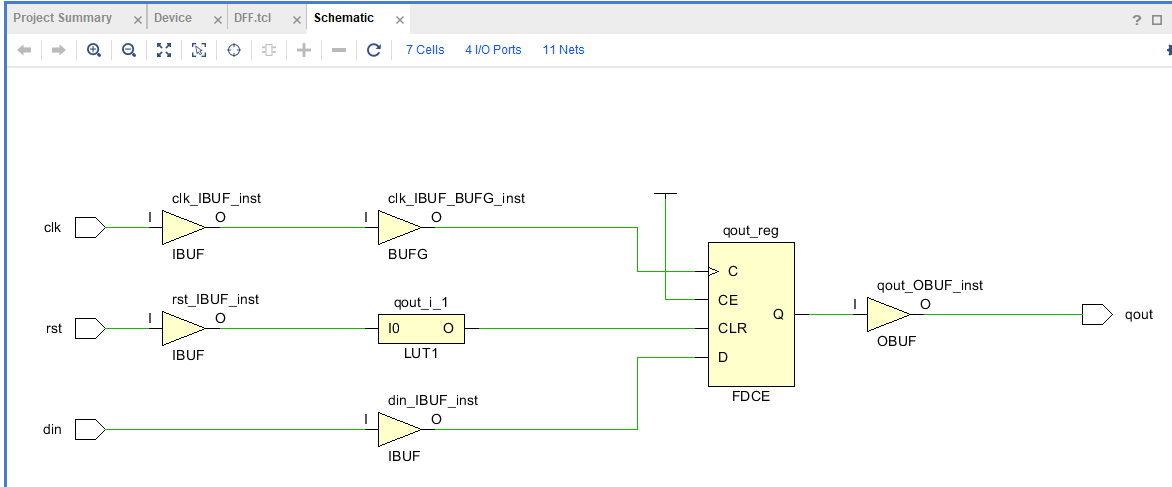

- D - Flip Flop 1

-Single D-Flip Flop

-> D-Flip Flop을 이용하여 1-bit input signal 입력신호의 Edge 검출 회로 설계

module DFF(

input rst, clk,

input din,

output reg qout

);

always @ (negedge rst, posedge clk)

if (rst == 0)

qout <= 0;

else

qout <= din;

endmodule//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force clk {0 0ns} {1 25ns} -repeat_every 50ns

add_force din 0

run 100ns

add_force din 1

run 50ns

add_force din 0

run 20ns

add_force din 1

run 50ns

add_force din 0

run 50ns

add_force din 1

run 10ns

add_force din 0

run 150ns

add_force din 1

run 200ns

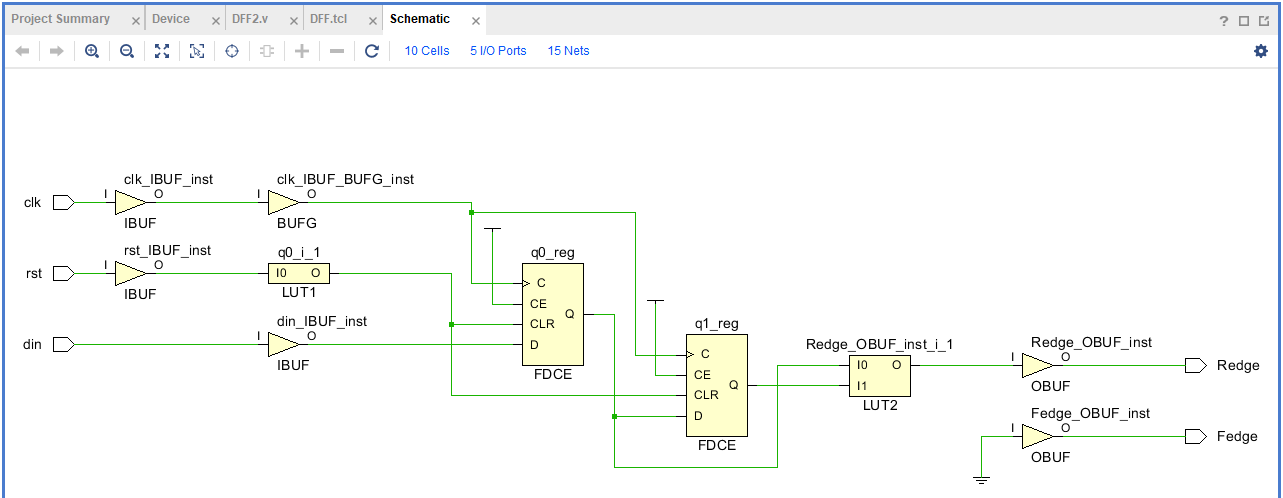

- D - Flip Flop 2

-> D-Flip Flop을 이용하여 1-bit input signal 입력신호의 Edge 검출 회로 설계

동작

->1bit 입력신호의 Edge를 검출하는 회로로, din신호를 두 개의 D-Flip Flop으로 Shift 시킨 후에 두 신호 q0와 q1에 대해 한 쪽을 not gate로 반전시켜서 AND

입력

- rst : Low 일 때 플립플롭의 출력을 0으로 묶어두는 Reset 입력

- clk : 100MHz 클럭 입력

- din : Edge를 검출할 신호 입력

출력

- Redge : din 신호의 rising edge에서 1 clock 구간동안 1을 출력하고 그 외에는 0을 출력

- Fedge : din 신호의 falling edge에서 1 clock 구간동안 1을 출력하고 그 외에는 0을 출력

내부 신호

- q0 : din 입력 신호를 clk 로 catch 한 플립플롭 출력신호

- q1 : q0 신호를 clk 로 catch 한 플립플롭 출력신호

동작개요

- 입력 din 을 2단의 플립플롭을 거치도록 하여 q0 , q1 을 생성

- q0 , q1 을 조합하여 redge 신호와 fedge 신호를 assign 문과 조합회로를 사용하여 edge

검출 기능 생성

//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force clk {0 0ns} {1 25ns} -repeat_every 50ns

add_force din 0

run 100ns

add_force din 1

run 50ns

add_force din 0

run 20ns

add_force din 1

run 50ns

add_force din 0

run 50ns

add_force din 1

run 10ns

add_force din 0

run 150ns

add_force din 1

run 200ns

- Register 1

module reg8(

input rst, clk,

input [7:0] din,

output reg [7:0] qout

);

always @ (negedge rst, posedge clk)

if (rst == 0)

qout <= 0;

else

qout <= din;

endmodule//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force rst {0 0ns} {1 25ns} -repeat_every 50ns

add_force din -radix hex aa

run 100ns

add_force din -radix hex 11

run 40ns

add_force din -radix hex 2b

run 20ns

add_force din -radix hex c3

run 30ns

add_force din -radix hex ff

run 20ns

add_force din -radix hex 50

run 40ns

- Register 2

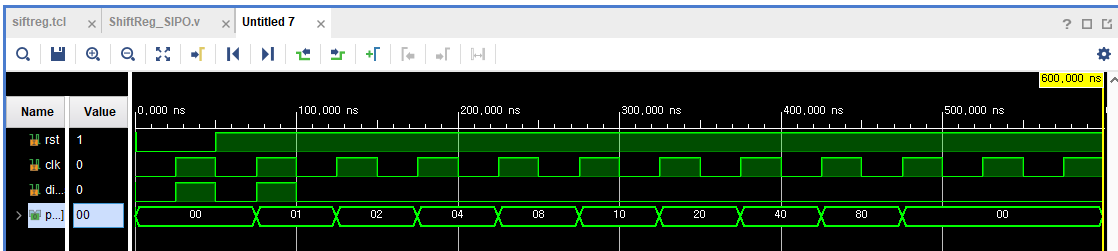

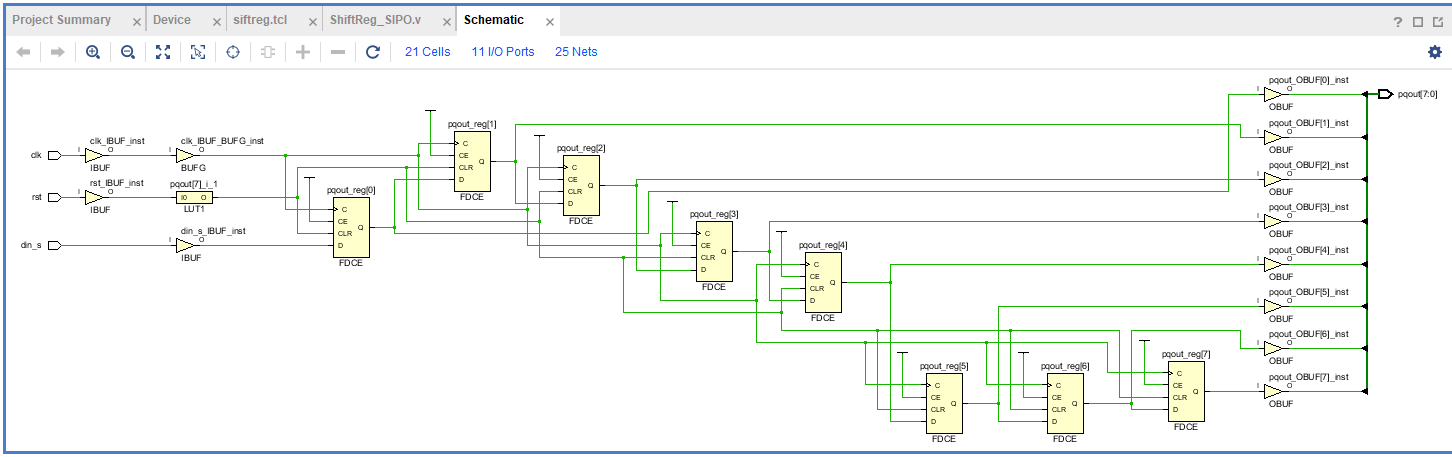

module ShiftReg_SIPO(

input rst, clk,

input din_s,

output reg [7:0] pqout

);

always @ (negedge rst, posedge clk)

if (rst == 0)

pqout <= 0;

else

pqout <= {pqout[6:0], din_s};

endmodule//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force clk {0 0ns} {1 25ns} -repeat_every 50ns

add_force din_s {0 0ns} {1 25ns} -repeat_every 50ns

run 100ns

add_force din_s {0 0ns} -repeat_every 50ns

run 500ns

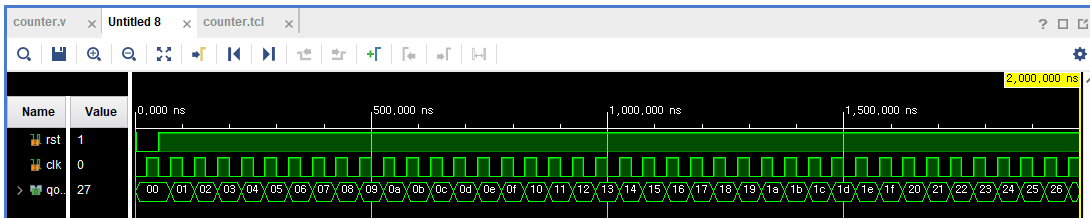

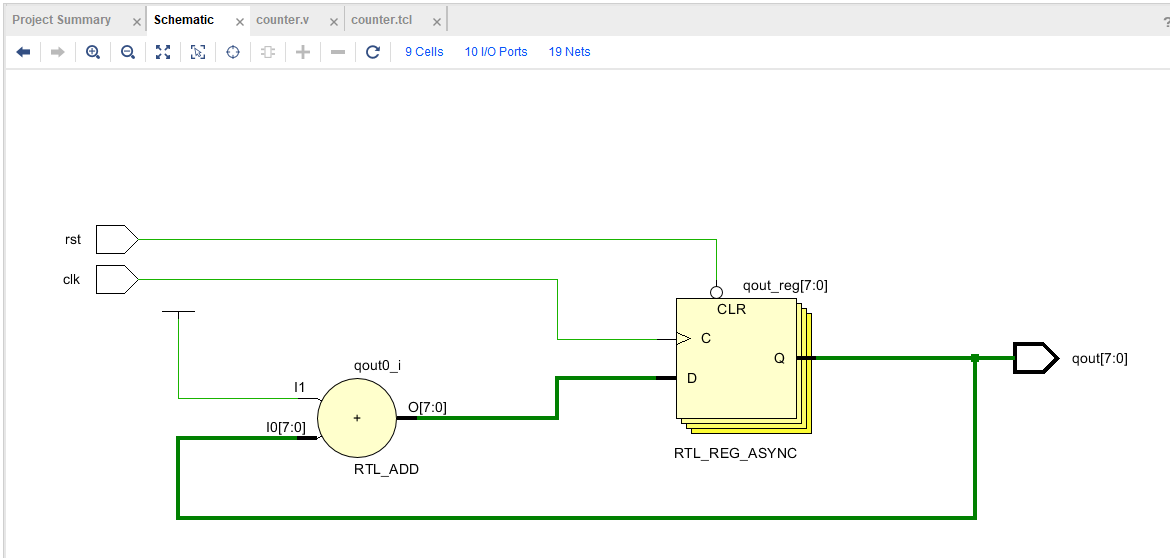

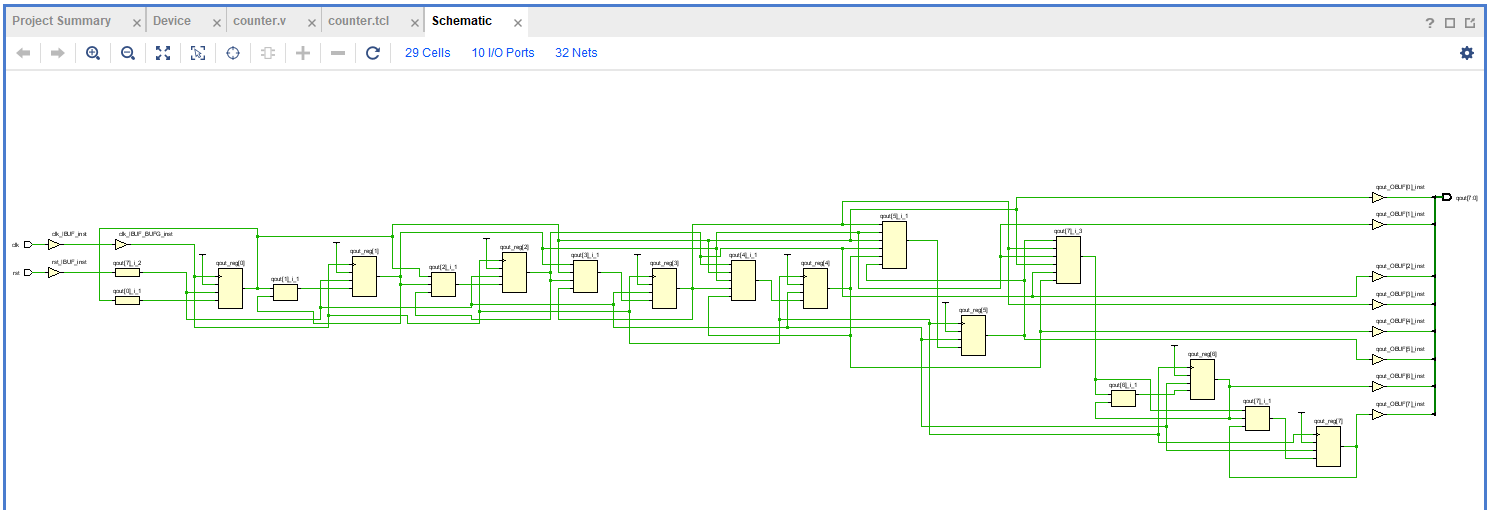

- 8bit Counter

8 bit binary counter 회로

-> 8 bit Register 의 현재 출력 값에 1을 더한 값을 다시 Register의 입력으로 인가하는 회로

-> 사용용도에 따라 다양한 형태의 카운터를 구성할 수 있으며, 형태가 달라도 사용되는 구문은 대부분 if 구문

동작

-> 8bit Register의 현재 출력 값에 1을 더한 값을 다시 Register의 입력으로 인가해 주는 것이 binary counter

- 8bit counter는 rst 신호가 low 일때 0으로 시작하여 매 clock 마다 1씩 증가하다가십진수로 255, 16진수로 ff 가 되면 다시 0으로 돌아가서 계속 count up

- [Count down] Count up 하는 counte에 더하기(+)를 빼기로(-)로 교체하면 ‘0’ 다음의 값은 십진수로 255가 되고 1씩 감소하여 ‘0’이 될때까지 감소하고 다시 255부터 감소

module counter(

input rst, clk,

output reg [7:0] qout

);

always @ (negedge rst, posedge clk)

if(rst == 0)

qout <= 0;

else

qout <= qout +1;

endmodule//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force clk {0 0ns} {1 25ns} -repeat_every 50ns

run 2us

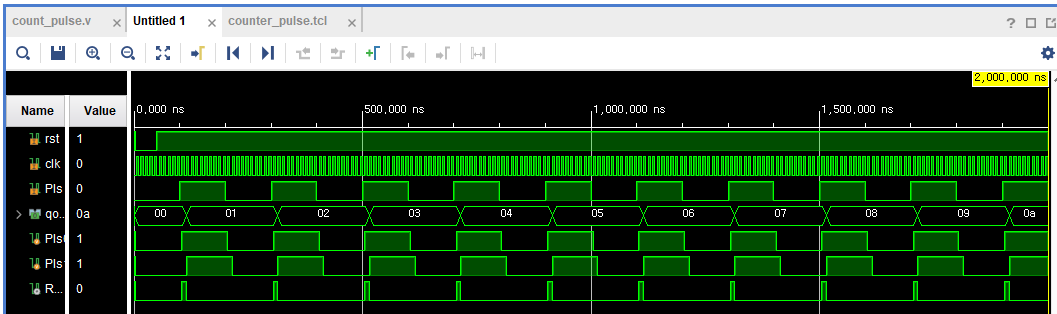

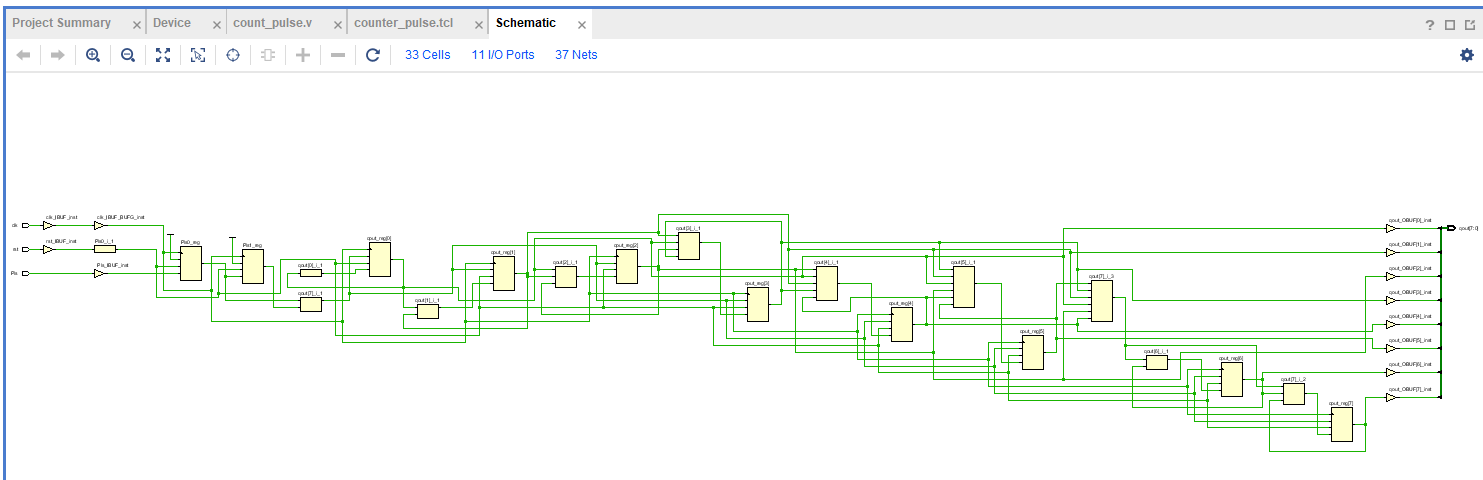

- Pulse Counter

Edge Detect 를 활용한 Pulse Counter회로

-> Pulse 입력을 받아서 Pulse 의 Rising Edge 에서 Count Up 하는 8 bit Counter

동작

Pulse 입력을 받아서 Pulse 의 Rising Edge 에서 Count Up 하는 8 bit Counter pls 입력을 받아서 2단의 D-Flip Flop을 거치면서 Pls0와 Pls1신호를 생성하고 Pls0가 ‘1’, Pls1이 ‘0’ 이 되는 Rising Edge에서 counter 값인 qout이 증가하는 회로

module count_pulse(

input rst, clk,

input Pls,

output reg [7:0] qout

);

reg Pls0, Pls1;

wire Redge;

always @ (negedge rst, posedge clk)

if(rst == 0)

begin

Pls0 <= 0;

Pls1 <= 0;

qout <= 0;

end

else

begin

Pls0 <= Pls;

Pls1 <= Pls0;

if(Redge == 1)

qout <= qout + 1;

end

assign Redge = Pls0& ~Pls1;

endmodule//tcl 코드

restart

add_force rst {1 0ns} {0 1ps} {1 50ns}

add_force clk {0 0ns} {1 5ns} -repeat_every 10ns

add_force Pls {0 0ns} {1 100ns} -repeat_every 200ns

run 2000ns

- Counter & Led

Counter 를 이용한 Led 제어

- 간단한 카운터를 이용하여 LED를 On/Off하는 기능 설계 및 보드 확인

- Test Bench 를 이용한 Simulation

module counter_led(

reset ,

clock ,

led

);

input reset;

input clock;

output [3:0] led;

reg [25:0] cnt;

always @ (posedge clock, negedge reset)

begin

if(reset == 0)

cnt <= 26'd0;

else

cnt <= ( cnt == 26'd0 ) ? 26'd0 : cnt+1'b1;

end

reg [3:0] led;

always @ (posedge clock, negedge reset)

begin

if(reset == 0)

led <= 4'b0;

else

led <= (cnt == 26'd500000) ? led + 1'b1 : led;

end

endmodule//테스트벤치

module counter_led_tb(

);

reg reset, clock;

initial

begin

reset = 0;

clock = 0;

#10 reset = 1;

end

always #5 clock = ~clock;

wire [3:0] led;

counter_led counter_led_u1(

.reset (reset),

.clock (clock),

.led (led)

);

endmodule

'[Harman] 세미콘(semiconductor) 아카데미-반도체설계 > Verilog를 이용한 RTL 시스템 반도체 설계' 카테고리의 다른 글

| FND&디코더 (0) | 2023.06.15 |

|---|---|

| 7-세그먼트 디코더, 크기 비교기 (0) | 2023.06.09 |

| 설계, 가산기, 디코더, 인코더, 스위칭 인코더 (0) | 2023.06.08 |

| 조합회로, 순차회로, Multiplexer (0) | 2023.06.02 |

| vivado, AND 게이트 (1) | 2023.06.01 |